在AI发展的海浪中白虎 色情,一项期间正在从“幕后”走向“台前”,也便是半导体先进封装(advanced packaging)。这项期间大约在单个建设内集成不同功能、制程、尺寸、厂商的芯粒(chiplet),以机动性强、能效比高、资本经济的样式打造系统级芯片(SoC)。因此,越来越多的AI芯片厂商疼爱这项期间。

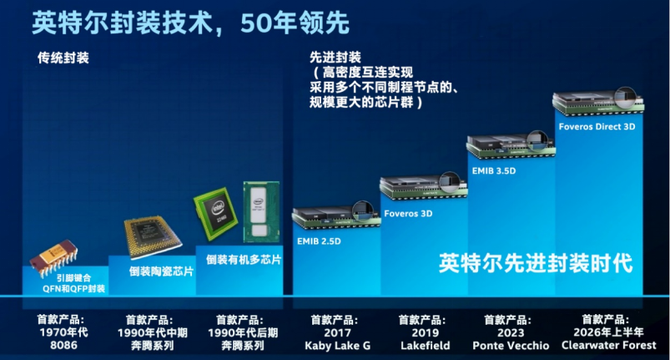

英特尔自本世纪70年代起捏续立异,深耕封装期间,蓄积了进步50年的丰富讲明注解。面向AI时期,英特尔正在与生态系统伙伴、基板供应商相助,共同制定尺度,引颈统共这个词行业应用先进封装期间。秉捏“系统工艺协同优化”(STCO)的理念,英特尔代工不仅大约向客户提供传统的封装、互连、基板等期间,还涵盖了系统级架构和联想干事,以及热管制和功耗管制等全观念辅助职责。

丰富全面的期间组合

英特尔代工的先进系统封装及测试(Intel Foundry ASAT)的期间组合,包括FCBGA 2D、FCBGA 2D+、EMIB 2.5D、EMIB 3.5D、Foveros 2.5D & 3D和Foveros Direct 3D等多种期间。

左上:FCBGA 2D、右上:EMIB 2.5D、左下:Foveros 2.5D & 3D、右下:EMIB 3.5D

· FCBGA 2D是传统的有机FCBGA(倒装芯片球栅格阵列)封装,适用于资本敏锐、I/O数目较少的家具。

· FCBGA 2D+在此基础上加多了基板层叠期间(substrate stacking),大约减少高密度互连的面积,镌汰资本,终点合乎荟萃和交换建设等家具。

· EMIB(镶嵌式多芯片互连桥接)2.5D期间通过基板内的小型硅桥设备芯片,适用于高密度的芯片间设备,在AI和高性能盘算(HPC)限制发扬出色。

· EMIB 3.5D则在此基础上引入了3D堆叠期间,芯片不错垂直堆叠在有源或无源的基板上,再通过EMIB期间设备,加多了堆叠的机动性,大约把柄IP的特色弃取垂直或水平堆叠,同期幸免使用大型的中介层。

· Foveros 2.5D和3D期间弃取基于焊料的设备样式,而不是基底设备,合乎高速I/O与较小芯片组辞别的联想。

· Foveros Direct 3D期间则通过铜和铜径直键合,终了更高的互连带宽和更低的功耗,从而提供不凡的性能。

值得提防的是,这些期间并非互斥,而是在一个封装中不错同期弃取,为复杂芯片的联想提供了极大的机动性。在生意层面,这体现了英特尔对封装细分市集的留意。

EMIB:AI芯片封装的理思弃取

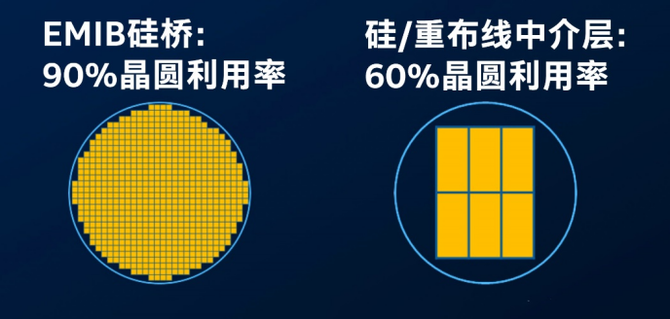

针对AI芯片的先进封装需求,与业界其它晶圆级2.5D期间,举例硅中介层、重布线层(RDL)比较,EMIB 2.5D期间具有诸多上风。

第 一,资本效益。EMIB期间弃取的硅桥尺寸相配小,比较于传统的大尺寸中介层,制造时能更高效地欺诈晶圆面积,减少空间和资源的铺张,概述股本更低。

第二,良率提高。EMIB期间不详了晶圆级封装(wafer level assembly)这一步伐,减少了模具、凸点等复杂工艺带来的良率死亡风险,从而提高了举座坐褥经由的良率。

第三,坐褥成果。与晶圆级期间比较,EMIB期间的制造步伐更少、复杂度更低,因此坐褥周期更短,大约为客户节俭可贵的期间。在市集动态快速变化的情况下,这种期间上风大约匡助客户更快地获取家具考据数据,加快家具上市。

第四,尺寸优化。晶圆级期间需要在基板上方添加中介层,而EMIB则将硅桥镶嵌基板,极地面提高了基板面积的欺诈率。同期,基板的尺寸与集成电路面板的神志相匹配,弃取EMIB大约在单个封装中集成更多芯片,从而容纳更多的职责负载。

第五,供应链与产能。英特尔领有熟识的供应链和填塞的产能,确保了EMIB大约知足客户对先进封装处治决议的需求。

瞻望将来

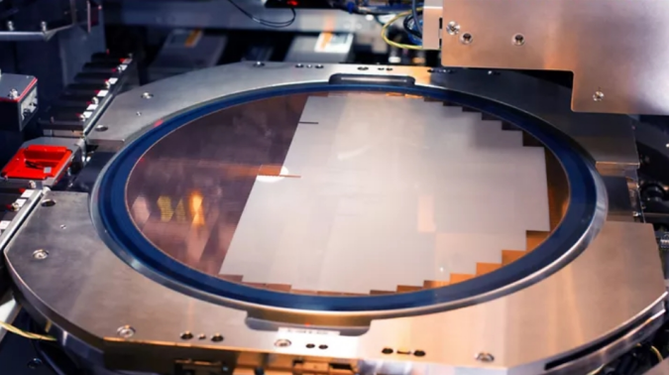

英特尔正在研发120×120毫米的超大封装,并操办在将来几年内向市集推出玻璃基板(glass substrate)。与现在弃取的有机基板比较,玻璃基板具有超低平面度、更好的热踏实性和机械踏实性等独有性能,大约大幅提高基板上的互连密度,为AI芯片的封装带来新的冲破。

英特尔在AI时期的先进封装期间限制赓续立异白虎 色情,将连续引颈和鼓励行业发展,为公共半导体产业注入新的活力。